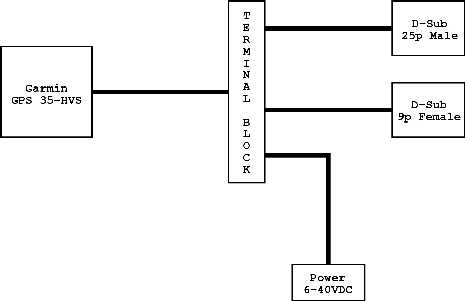

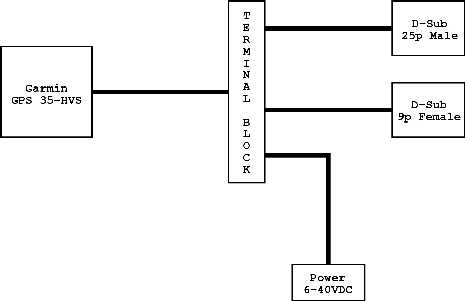

System block diagram

This page describes the interface

circuit which is used at seismological stations running

SEISLOG at Institute of Solid Earth Physics, University

of Bergen.

The interface is used between a GPS and a PC. The PC is

running SEISLOG-software and the GPS (Garmin GPS 35-HVS)

is providing accurate synchronization of the PC's real-time

clock.

The GPS outputs NMEA0183 messages (GPGGA & GPRMC) at

9600 baud. It also has an output called 1PPS (meaning One

Pulse Per Second). NMEA messages are output at RS-232

levels and is directly connected to one of the PC's COM-ports.

The 1PPS signal is (by default) a positive pulse of 100ms.

Voltage levels are 4.4V and 0V for logical high and low,

respectively. Output impedance is 250 ohm. If this signal

is directly connected to a PC parallel port input with

internal pull-ups (most PCs have internal pull-ups at

approx. 1 kohm) the voltage levels will be pulled to 4.5V

and 1V for high and low. The high level is OK, but the

low level is out of specification for TTL-signals. Low

level should be maximum 0.8V at an input, but in order to

obtain required noise margins a TTL-output shall not

deliver more than 0.4V.

The OCCC solves this problem by adding an emitter-follower

buffer to the 1PPS signal. The transistor used is a PNP

germanium transistor (AC128). The voltage levels at the

PC's parallel port (or at the Emitter of transistor) is 4.6V

and 0.2V for high and low, respectively.

If the OCCC is used in a very noisy environment one

should keep in mind that germanium transistors are

sensitive to high voltages. Some kind of EMP-protection (transient

diodes) may be added at Basis of the transistor.

The original schematic diagram has been

scanned and is available as an Adobe Acrobat PDF-file.

Click to download:

occc.pdf

Here is also the GPS 35 "Technical

Specification".

There may be a newer revision available at Garmin's WWW-site.

|

|

Click the icons below to see full-size

images of the different parts of the interface.

|